ในช่วงกลางปี ค.ศ.1990 โพรเซสเซอร์ทีการออกแบบสถาปัตยกรรมแยกออกเป็นสองรูปแบบ ได้แก่

- สถาปัตยกรรมแบบ CISC (Complex Instruction Set Computer)

- สถาปัตยกรรมแบบ RISC (Reduced Instruction Set Computer)

โดยสถาปัตยกรรมการออกแบบซีพียูนั้นมีผลต่อการทำงานของคอมพิวเตอร์เป็นอย่างมาก และในบทความนี้จะพูดถึง สถาปัตยกรรมแบบ RISC (Reduced Instruction Set Computer)

คำว่า RISC ย่อมาจาก ” Reduced Instruction Set Computer ” เป็นแผนการออกแบบ CPU ตามคำสั่งง่ายๆและทำงานได้อย่างรวดเร็ว

สถาปัตยกรรม RISC คืออะไร : คอมพิวเตอร์ชุดคำสั่งแบบย่อคือคอมพิวเตอร์ที่ใช้เฉพาะคำสั่งง่ายๆที่สามารถแบ่งออกเป็นคำสั่งต่างๆเพื่อให้ได้การทำงานระดับต่ำภายในรอบ CLK เดียวเนื่องจากชื่อของมันเสนอว่า “Reduced Instruction Set”

RISC เป็นไมโครโปรเซสเซอร์คอมพิวเตอร์ชุดคำสั่งแบบลดขนาดและสถาปัตยกรรมประกอบด้วยชุดคำสั่งที่ได้รับการปรับแต่งอย่างมาก หน้าที่หลักของสิ่งนี้คือการลดเวลาในการดำเนินการคำสั่งโดย จำกัด และปรับจำนวนคำสั่งให้เหมาะสม ดังนั้นแต่ละรอบคำสั่งจะใช้วงจรนาฬิกาเดียวซึ่งทุกรอบนาฬิกาจะมีพารามิเตอร์สามตัว ได้แก่ การดึงข้อมูลถอดรหัสและดำเนินการ

ประเภทของโปรเซสเซอร์ส่วนใหญ่จะใช้เพื่อดำเนินการคำสั่งที่ยากหลายคำสั่งโดยการรวมเข้าด้วยกันเป็นคำสั่งที่ง่ายกว่า โปรเซสเซอร์ RISC ต้องการทรานซิสเตอร์จำนวนมากในการออกแบบและช่วยลดเวลาการเรียนการสอนสำหรับการดำเนินการ ตัวอย่างที่ดีที่สุดของโปรเซสเซอร์ RISC ได้แก่ PowerPC, SUN’s SPARC, RISC-V, Microchip PIC processors เป็นต้น

หลักการอย่างง่าย ๆ ของคอมพิวเตอร์แบบ RISC คือ มีการออกแบบให้ซีพียูทำงานในวงรอบของสัญญาณนาฬิกา (Cycle) ที่แน่นอนโดยพยายามลดจำนวนคำสั่งลงให้เหลือเป็นคำสั่งพื้นฐานมากที่สุด แล้วใช้หลักการไปป์ไลน์ (Pipeline) คือ การทำงานแบบคู่ขนานชนิดเหลื่อมกัน (Overlap) โดยปกติแล้วการทำงานใน 1 ชุดคำสั่งจะใช้เวลามากกว่า 1 วงรอบสัญญาณนาฬิกา โดยในการทำคำสั่งเหล่านั้นมีการทำงานในลักษณะแถว (Pipe) และทำงานขนานกัน จึงทำให้ได้ค่าเฉลี่ยโดยรวมของเวลาเป็นคำสั่งละ 1 วงรอบสัญญาณนาฬิกา

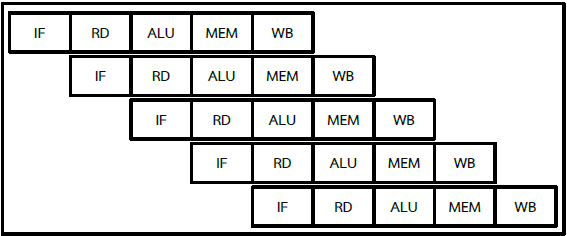

เช่น สถาปัตยกรรมคอมพิวเตอร์แบบ RISC ได้แก่ MIPS รุ่น R2000 ได้มีการออกแบบชุดคำสั่งไว้อย่างชัดเจนว่ามีการทำงานแบบ 5 ขั้นตอน นั่นคือเป็นการทำงานแบบขนาน 5 ระดับด้วยกันคือ

IF Instruction Fetch เป็นการเฟทช์คำสั่ง หรือดึงข้อมูลจากหน่วยความจำ

RD Read เป็นการอ่านโอเปอแรนด์ (Operand) จากรีจิสเตอร์ในซีพียู

ALU เป็นการคำนวณในหน่วยคำนวณและตรรกศาสตร์ตามคำสั่งนั้น ๆ

MEM การติดต่อกับหน่วยความจำ

WB การเขียนข้อมูลผลลัพธ์ลงในรีจิสเตอร์

ภาพแสดงการใช้คำสั่งแบบ 5 ระดับใน R2000

วิธีการทางานของคำสั่งแบบคู่ขนานเช่นนี้ แสดงได้จากภาพ ซึ่งจะมีผลทาให้การทางานของคาสั่งเสร็จสิ้นได้ใน 1 วงรอบของสัญญาณนาฬิกา (Cycle) จากภาพ จะใช้เวลาถึง 5 วงรอบสัญญาณนาฬิกา (Cycle) แต่ทุกช่วงการทางานซีพียูจะทางานขนานกับทั้ง 5 ส่วนนี้ด้วย ขณะที่เฟทช์คาสั่งหนึ่งอยู่ภายในก็มีการทา RD, ALU, MEM และ WB ของแต่ละคาสั่งที่ผ่านมา ดังนั้นการเฟทช์จึงเกิดขึ้นได้ทุกวงรอบ

– – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – –

ข้อดีของโปรเซสเซอร์ RISC มีดังต่อไปนี้

“แผนผังสวิตช์ไฟสองทาง ”

- การออกแบบ CPU ทำได้ง่ายกว่าและใช้กำลังไฟน้อยกว่า

- ประสิทธิภาพของโปรเซสเซอร์นี้ดีเนื่องจากมีข้อ จำกัด และง่าย ของชุดคำสั่ง

- โปรเซสเซอร์นี้ใช้ทรานซิสเตอร์หลายตัวในการออกแบบเพื่อให้มีราคาถูกลง

- โปรเซสเซอร์ RISC ช่วยให้คำสั่งใช้พื้นที่เปิดโล่งบนไมโครโปรเซสเซอร์เนื่องจากความเรียบง่าย

- มันง่ายมากเมื่อเทียบกับโปรเซสเซอร์อื่นด้วยเหตุนี้จึงสามารถทำงานให้เสร็จภายในรอบนาฬิกาเดียว

ข้อเสียของโปรเซสเซอร์ RISC มีดังต่อไปนี้

- ผู้พัฒนาโปรแกรมส่วนใหญ่ใช้สถาปัตยกรรมแบบ CISC มากกว่าเนื่องจากเหตุผลทางการตลาด

- ตลาด CPU ส่วนใหญ่เป็นของ Intel

- ประสิทธิภาพของโปรเซสเซอร์นี้อาจเปลี่ยนแปลงไปตามโค้ดที่เรียกใช้งานเนื่องจากคำสั่งถัดไปอาจขึ้นอยู่กับคำสั่งก่อนหน้านี้สำหรับการนำไปใช้งานภายในรอบ

- คำสั่งที่ซับซ้อนมักใช้โดยคอมไพเลอร์และโปรแกรมเมอร์

โปรเซสเซอร์เหล่านี้ต้องการหน่วยความจำที่รวดเร็วมากเพื่อเก็บคำสั่งต่างๆที่ใช้หน่วยความจำแคชจำนวนมากเพื่อตอบสนองต่อคำสั่งภายในเวลาที่น้อยลง